Texas Instruments LMX1204 Bruksanvisning

Texas Instruments ej kategoriserat LMX1204

Läs gratis den bruksanvisning för Texas Instruments LMX1204 (72 sidor) i kategorin ej kategoriserat. Guiden har ansetts hjälpsam av 5 personer och har ett genomsnittsbetyg på 4.1 stjärnor baserat på 3 recensioner. Har du en fråga om Texas Instruments LMX1204 eller vill du ställa frågor till andra användare av produkten? Ställ en fråga

Sida 1/72

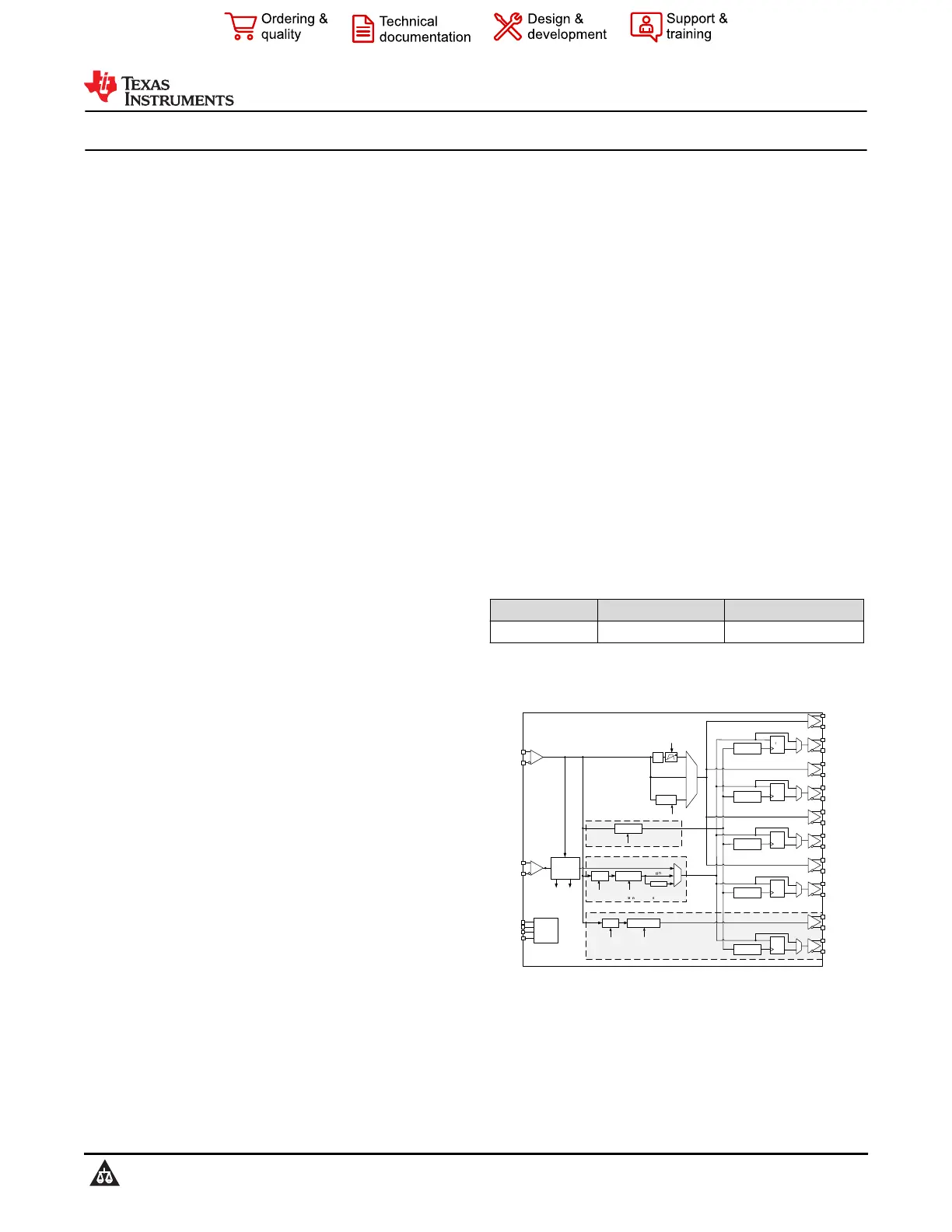

LMX1204 Low-Noise, High-Frequency JESD Buffer/Multiplier/Divider

1 Features

•300MHz to 12.8GHz output frequency

•Ultra-low noise

–Noise floor of –161dBc/Hz at 6GHz output

–1/f Noise of –154dBc/Hz at 6GHz output, 10kHz

offset

–5fs jitter (12kHz to 20MHz)

–<30fs additive jitter (DC to f

CLK

)

•4 high-frequency clocks with corresponding

SYSREF outputs

–Shared divider that supports ÷1 (buffer mode),

÷2, 3, 4, 5, 6, 7, and 8

–Shared PLL-based multiplier that supports p1-x1

(filter mode), x2, x3, and x4

•LOGICLK and corresponding SYSREF outputs

–On separate divide bank

–÷1, 2, 4 pre-divider

–÷1 (bypass), 2, …, 1023 post divider

•8 programmable output power levels

•Synchronized SYSREF clock outputs

–508 delay step adjustments of less than 2.5ps

each at 12.8GHz

–Generator and repeater modes

–Windowing feature for SYSREFREQ pins to

optimize timing

•SYNC feature to all divides and multiple devices

•2.5V operating voltage

•–40ºC to 85ºC operating temperature

2 Applications

•Test & Measurement:

–Oscilloscope

–Wireless equipment testers

–Wideband digitizers

•Aerospace & Defense:

–Radar

–Electronic warfare

–Seeker Front end

–Munitions

–Phase array antenna / Beam forming

•General Purpose:

–Data converter clocking

–Clock buffer distribution / division

3 Description

The high-frequency capability and extremely low jitter

of this device, makes a great approach to clock

precision, high-frequency data converters without

degradation to the signal-to-noise ratio. Each of the

four high-frequency clock outputs, and additional

LOGICLK output with larger divider range, is paired

with a SYSREF output clock signal. The SYSREF

signal for JESD interfaces can either be internally

generated or passed in as an input and re-clocked

to the device clocks. For data converter clocking

applications, having the jitter of the clock be less than

the aperture jitter of the data converter is critical. In

applications where more than four data converters

must be clocked, a variety of cascading architectures

can be developed using multiple devices to distribute

all the high-frequency clocks and SYSREF signals

required. With low jitter and noise floor, this device

combined with an ultra-low noise reference clock

source is an exemplary selection for clocking data

converters, especially when sampling above 3GHz.

Package Information

PART NUMBERPACKAGE

(1)

PACKAGE SIZE

(2)

LMX1204RHA (VQFN, 40)6.00mm × 6.00mm

(1)For more information, see Section 11.

(2)The package size (length × width) is a nominal value and

includes pins, where applicable.

CLKOUT0

SYSREFOUT0

CLKIN

SYSREFREQ

÷1,2,4

rb_CLKPOS

xM

CAL

÷2,3,..,8

÷1,2,3,...1023

÷1,2,4÷2,3,..4095

Pulser

÷2,4,8,16

Phase

Interpolator

CLKOUT1

SYSREFOUT1

CLKOUT2

SYSREFOUT2

CLKOUT3

SYSREFOUT3

LOGICLKOUT

LOGISYSREFOUT

Repeater

SYSREF

Windowing

and Capture

RESET

RESET

RESET

RESET

RESET

Con

nous

SYSREF Genera

on & Distribu

on

0

Phase

Interpolator

1

Phase

Interpolator

2

Phase

Interpolator

3

Phase

Interpolator

4

IQ Phase Interpolator

Divider

Logic Clock & Logic SYSREF

RESETRESET

Digital

Control

MUXOUT

CS#

SDI

SCK

Block Diagram

LMX1204

SNAS800B – JULY 2021 – REVISED FEBRUARY 2024

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Produktspecifikationer

| Varumärke: | Texas Instruments |

| Kategori: | ej kategoriserat |

| Modell: | LMX1204 |

Behöver du hjälp?

Om du behöver hjälp med Texas Instruments LMX1204 ställ en fråga nedan och andra användare kommer att svara dig

ej kategoriserat Texas Instruments Manualer

3 April 2026

31 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

5 Mars 2026

ej kategoriserat Manualer

Nyaste ej kategoriserat Manualer

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026

3 April 2026